-

Notifications

You must be signed in to change notification settings - Fork 46

Acceptance Test Project

This page describes how to set up the NetFPGA-SUME board and run the initial Acceptance Test. The Acceptance Test verifies that your board is working correctly. You should run the Acceptance Test before attempting any development with a new NetFPGA-SUME board. If the tests indicate a problem with your board, return it immediately to your distributor.

The Acceptance Test is performed by the NetFPGA-SUME’s Virtex7 FPGA. The status of the tests is displayed using a python-based GUI. An Acceptance Test suite, containing the hw design along with supporting software, is provided in the NetFPGA-SUME github repository under the projects/acceptance_test/ subdirectory.

By default, the Acceptance Test checks on board interfaces and the SFP+ interfaces. The Acceptance Test provides cover for all interfaces, however some interfaces require additional hardware for testing. We provide more information about this below.

Note : Please make sure that you have followed the installation procedure as mentioned in the Reference Operating System Setup Guide before running the test (e.g. sufficient privileges to access serial ports and a patched pySerial), and make sure to have root privileges.

The NetFPGA Production Test is run in Server Mode, wherein the NetFPGA-SUME board is installed as PCIe expansion card in a host PC, allowing most major on-board systems to be verified.

- Clone the NetFPGA SUME development repository using the following command

git clone https://github.com/NetFPGA/NetFPGA-SUME-live.git

- Source the Xilinx Vivado tools

source /{installation_directory}/Vivado/2014.4/settings64.sh

-

Edit the

NetFPGA-SUME-live/tools/settings.shfiles to export paths based on your installation directory. -

Source the updated settings.sh

source NetFPGA-SUME-live/tools/settings.sh

- Go to the acceptance project folder

cd NetFPGA-SUME-live/projects/acceptance_test/

- Build the IP cores for the acceptance test by running the following command

make cores

- Then you can run the Test GUI by running

make test

-

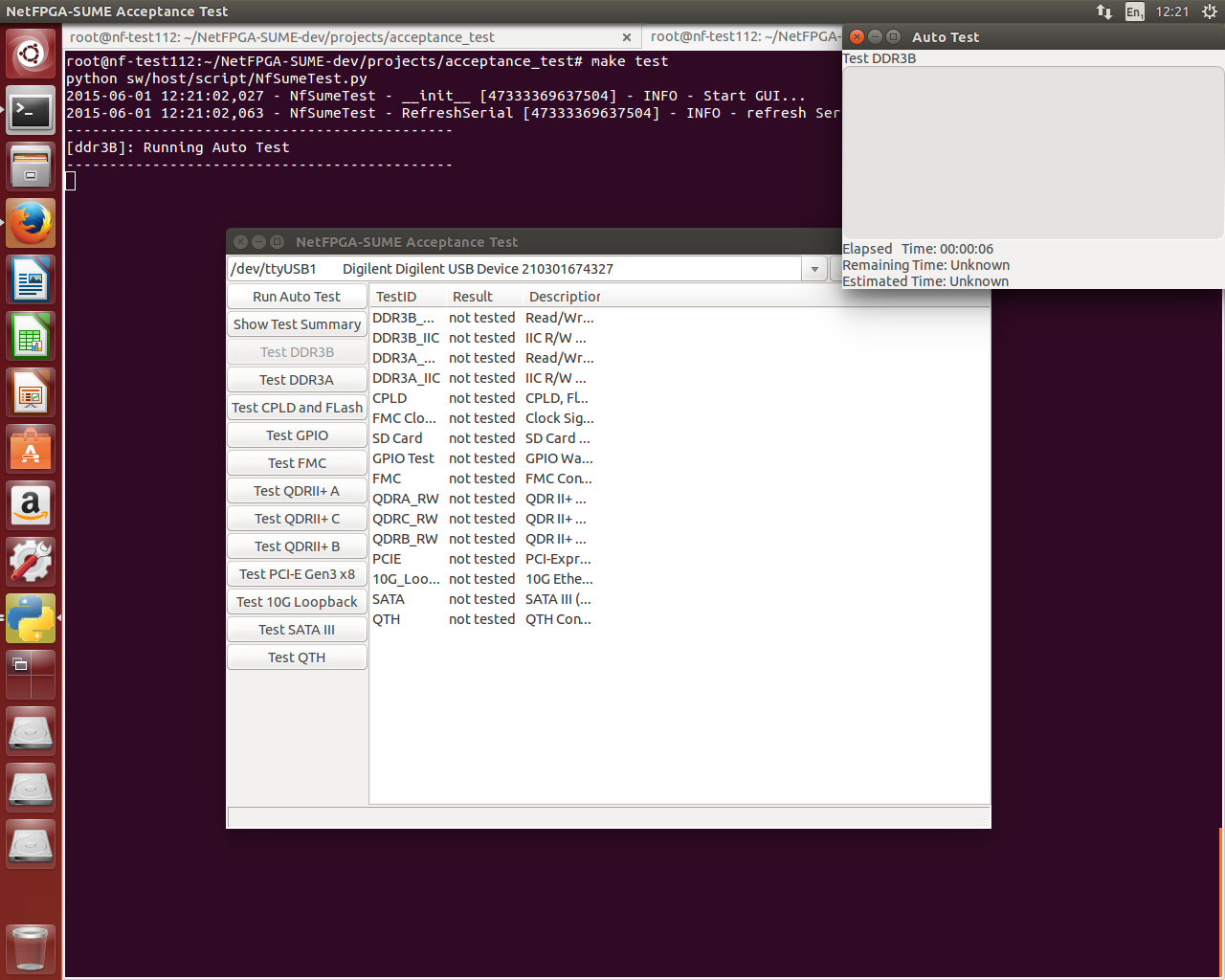

The NetFPGA-SUME Acceptance test GUI will pop up. Choose the right serial interface as shown below

-

Click the start button (as shown below) and the GUI will show all the tests available

-

You can click the "Run Auto Test" button to start the the default test. If any of the bit files are missing, the test will automatically generate them. Note: When starting with a clean repository w/o any bitfiles, this will open a bunch of new windows where you can see the generation one at a time.

-

Once the default tests are executed, the status of the tests can be viewed under the Results section.

-

Acceptance tests The acceptance test is composed of a set of default tests and several optional tests.

Acceptance Test

├── Default Test

│ └── DDR3 A/B Tests

│ └── QDR A/B/C Tests

│ └── 10G Ethernet Loopback Test

│ └── CPLD and Flash Test

├── Optional Tests

│ └── PCI-E Loopback Test

│ └── FMC Loopback Test

│ └── QTH Loopback Test

│ └── GPIO/IIC/UART General Test

│ └── SATA Loopback Test

- The default tests include the following projects:

├── Default Test

│ └── DDR3 A/B Tests

│ └── QDR A/B/C Tests

│ └── 10G Ethernet Loopback Test

│ └── CPLD and Flash Test

The 10G Ethernet Loopback Test requires fibers and 10G SFP+ transceivers. The test requires an external loopback connection, where port 0 is connected to port 1, and port 2 is connected to port 3.

**Note: While running the memory tests (DDR's and QDR's), a test may occasionally fail (known issue). Try running the test a second time. **

- Optional tests (covered by the Acceptance Test) require dedicated hardware and cables. Some of the hardware required can be easily acquired by users (e.g. a SD card or a crossed SATA cable), other adapters are currently not widely available, though we hope to make their design available online. Information about the cables is provided in the next section.

├── Optional Test

│ └── PCI-E Loopback Test

│ └── FMC Loopback Test

│ └── QTH Loopback Test

│ └── GPIO/IIC/UART General Test

│ └── SATA Loopback Test

The above figure shows the standalone acceptance test along with the loopback boards and other test interfaces connected.

Implementation details of the acceptance test are provided in a dedicated page. The implementation page also includes instructions on running the test in non-gui mode.

Question: I am trying to run the acceptance test, but it fails, I get a log with an error of the form:

2015-06-24 18:21:49,264 - NfSumeTest - __init__ [47755026647680] - INFO - Start GUI...

2015-06-24 18:21:49,325 - NfSumeTest - RefreshSerial [47755026647680] - INFO - refresh Serial Ports

2015-06-24 18:22:00,399 - NfSumeTest - RefreshSerial [47755026647680] - INFO - refresh Serial Ports

Create Progress

---------------------------------------------

[ddr3B]: Running Auto Test

---------------------------------------------

Exception in thread Thread-1:

Traceback (most recent call last):

File "/usr/lib/python2.7/threading.py", line 810, in __bootstrap_inner

self.run()

File "sw/host/script/NfSumeTest.py", line 907, in run

File "sw/host/script/NfSumeTest.py", line 436, in TestInterface

File "sw/host/script/NfSumeTest.py", line 562, in ProgramFpga

File "/usr/lib/python2.7/subprocess.py", line 710, in __init__

errread, errwrite)

File "/usr/lib/python2.7/subprocess.py", line 1327, in _execute_child

raise child_exception

OSError: [Errno 2] No such file or directory

Answer: The Vivado tool change is not sourced, or you do not have root privileges. Source the Xilinx Vivado tools:

source /{installation_directory}/Vivado/2014.4/settings64.sh

Question: The DRAM / QDR test has failed, what should I do?

Answer: Try running the test again (refer to this). The failure is typically caused by a failure of the calibration init process, which is part of the Xilinx memory interface generated (MIG) core. If the problem persists - contact the manufacturer.

Question: My board consistently fails the acceptance test, what should I do?

Answer: You should report the issue back to Digilent, at [email protected], and ask for a board replacement.

Qusetion: The GUI fails to open / I receive errors regarding the python script / I receive errors regarding Widgets

Answer: Please check that you have installed all the required packages, as instructed on the Setup Guide. Alternatively, you can run the test in non-GUI mode.

cd NetFPGA-SUME-live/projects/acceptance_test/sw/host/scripts

python ./NfSumeTest -nogui

Additional instructions on running the test without GUI or python are provided on the Acceptance Test Project Implementation page.

Question: How can I get the loopback cards required to run some of the tests?

Answers: Unfortunately, these boards were manufactured by Digilent only for the production of the board and are currently not available for sale. You can contact Digilent directly for further details. Note that for some of the tests only simple accessories are required in order to run the test:

- SD Card - Any MicroSD card will do

- SATA - You will need a cross over SATA cable

- GPIO - You will need a few jumpers

- PCIe - Several PCIe loopback boards are available from various vendors, we have no special recommendation